### DALHOUSIE UNIVERSITY Department of Electrical & Computer Engineering Digital Circuits - ECED 2200

# **Experiment 5 - Registers and Counters**

## **Objectives:**

- 1. To design a Serial in Parallel out register

- 2. To design a Ripple counter [2 bit] (count up/count down)

- 3. To design a Synchronous counter [2 bit]

## Theory:

### Registers:

A register is a device capable of storing and shifting binary data and is typically used as a temporary storage device. Registers consist of several stages with each stage being able to hold one bit. These stages consist of a flip-flop or some other type of storage device. Shift registers are generally characterized by the method bits are inputted and outputted. Serial input / serial output registers load the bits onto the register one at a time and output bits one at a time. Serial input / parallel output registers inputs bits one at a time but an output line is placed at the exit of each stage. So with a 4-stage register four outputs would be seen. For a parallel in / serial out register bits are inputted to each stage simultaneously but the output is just one bit at a time. In a parallel input / parallel output register bits are loaded into each stage simultaneously and the output of each stage is sent to individual output lines.

### Counters:

A counter is a device capable of counting electronic events such as clock pulses by progressing through a sequence of binary states. Counters usually consist of flip-flops and basic logic gates and can be asynchronous or synchronous. If the counter counts at unfixed times it is said to be asynchronous. These are commonly referred to as ripple counters. A synchronous counter is a counter that increments at a fixed time.

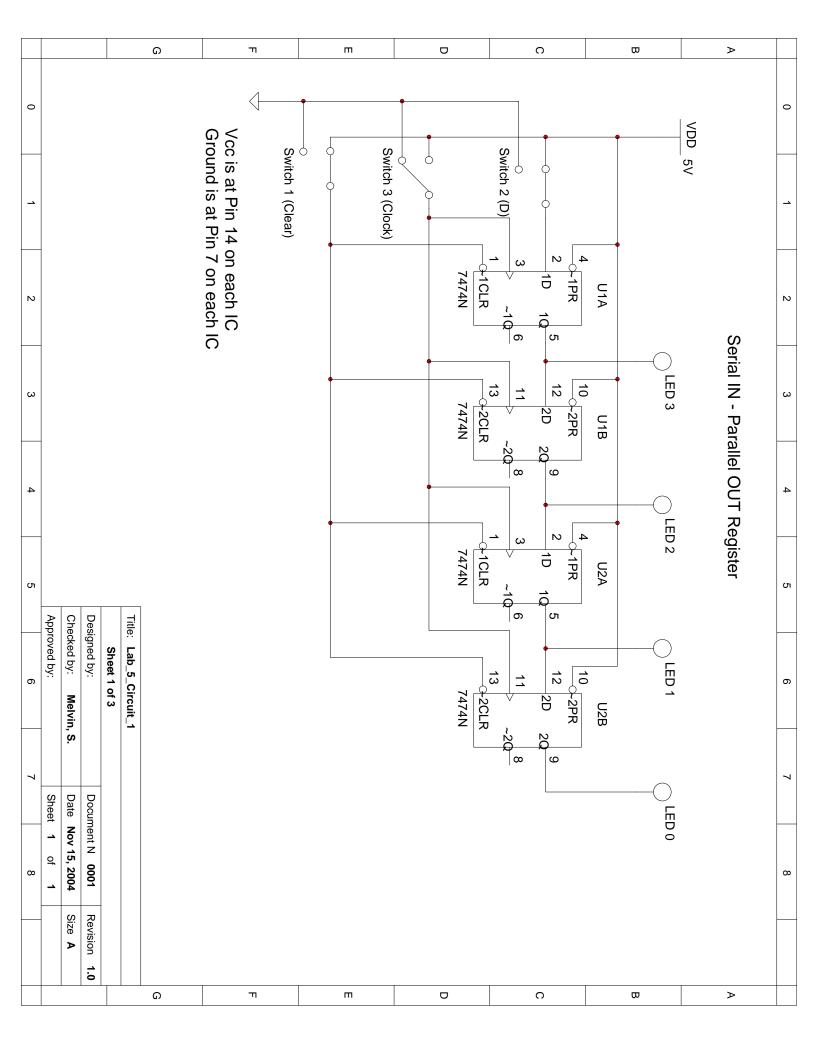

### Part 1. Serial in - Parallel out register

### **Procedure:**

Select an appropriate D flip-flop from Quartus II library, and implement a 4-bit serial in – parallel out register as shown on page 3. For this circuit:

1. While keeping the input constant, see what happens to the outputs with each clock transition

### Part 2. Ripple Counter

#### **Procedure:**

Select an appropriate JK flip-flop from Quartus II library and implement the 2-bit ripple counter circuit as shown on page 4. In this circuit L0 and L1 are counter outputs. For this circuit:

- 1. Setup the circuit to count up by setting switch 3 and switch 4 appropriately (see circuit diagram).

- 2. What happens to the output with each clock transition?

- 3. Setup the circuit to count down and repeat steps 1 and 2.

### Part 3. Synchronous Counter

#### **Procedure:**

Implement the circuit shown on page 5. In this circuit L0 and L1 are the counter outputs. Describe what happens to the output with each clock transition.

|   |                                                                          |                                                                                 |                                     | G                  | п                  | m                      | D        | n                | Φ                 | ⊳                                                                                  |   |

|---|--------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------|--------------------|--------------------|------------------------|----------|------------------|-------------------|------------------------------------------------------------------------------------|---|

| 0 | 0                                                                        |                                                                                 |                                     | (1                 | •                  | •                      | •        | •                |                   |                                                                                    | 0 |

| - | Ground is at l                                                           | /cc is at Pin                                                                   | Ground is at Pin 13 on IC 7476      | ✓<br>Vcc is at Pin | Switch 2 (Clear)   | •                      |          | Switch 5 (Clock) | Switch 1 (Preset) | VDD 5V                                                                             |   |

| 2 | Pin 7 on IC                                                              | 14 on IC 74(                                                                    | Pin 13 on IC                        | 5 on IC: 747       |                    |                        | 72       | ω 16             | 4 N               |                                                                                    | 2 |

| ω | Ground is at Pin 7 on IC 7408 & IC 7432                                  | Vcc is at Pin 14 on IC 7408 & IC 7432<br>Ground is at Pin 7 on IC 7408 & IC 743 | C 7476                              | ກັ                 | Switch 4           |                        | 7476N    |                  | R 1A<br>15        | 2-Bit Ripple Counter                                                               | ω |

| 4 | 2                                                                        |                                                                                 |                                     |                    |                    |                        | Switch 3 | 7408N            | LED 0<br>U2A      | Counter                                                                            | 4 |

| ъ |                                                                          |                                                                                 |                                     |                    |                    | U3A<br>2<br>7432N<br>3 |          | <u>۳</u> س<br>س  | 2A                |                                                                                    | л |

| 6 | Checked by:<br>Approved by:                                              | Designed by:                                                                    | Title: Lab_5_Circuit_2 Sheet 2 of 3 |                    | 8<br>2CLR<br>7476N | - 2K ~2Q               | 7<br>U1B |                  |                   | Switch 3 H<br>Switch 4 Hi                                                          | 6 |

| 7 | Melvin, S.                                                               | ivin, S. Docun                                                                  | Sircuit_2<br>of 3                   |                    |                    | 10                     |          |                  |                   | igh & Switch<br>gh & Switch                                                        | 7 |

| 8 | Date         Nov 15, 2004           Sheet         1         of         1 |                                                                                 |                                     |                    |                    |                        |          |                  |                   | Switch 3 High & Switch 4 Low: Count-Up<br>Switch 4 High & Switch 3 Low: Count-Down | 8 |

| 9 | 1 Size A                                                                 | 1 Revision 1.0                                                                  |                                     |                    |                    |                        |          |                  |                   | :-Down                                                                             | 9 |

|   |                                                                          |                                                                                 |                                     | G                  | П                  | т                      | σ        | n                | σ                 | ⊳                                                                                  |   |

|   |                                                             | E            | : |                                 | G                |  | τī |                | т                              | D                          | 0        | ω                   | ⊳ |    |

|---|-------------------------------------------------------------|--------------|---|---------------------------------|------------------|--|----|----------------|--------------------------------|----------------------------|----------|---------------------|---|----|

| 0 |                                                             |              |   |                                 |                  |  |    |                |                                |                            |          |                     |   | 0  |

|   | Vcc is at Pin 5 on IC 7476<br>Ground is at Pin13 on IC 7476 |              |   |                                 |                  |  |    |                |                                |                            |          |                     |   |    |

| 2 |                                                             |              |   |                                 | Switch 3 (Clear) |  | ā  | Switch 1 (Cloc | 5                              | -00<br>Switch 2 (Preset)   |          |                     | 2 |    |

| з |                                                             |              |   |                                 | ·                |  | -  | ž              | ω                              |                            | N        |                     |   | ы  |

| 4 |                                                             |              |   |                                 |                  |  |    |                | -1CLR<br>7476N<br>JK Flip Flop | 1K 10 10 15                |          | Synchronous Counter |   | 4  |

| 5 | Ap                                                          | D            |   | Title:                          |                  |  |    | ~              |                                |                            |          | unter               |   | сл |

| 6 | Checked by:<br>Approved by:                                 | Designed by: |   | e: Digital Circuits (ECED 2200) |                  |  |    |                | 2CLR<br>7476N<br>JK Flip Flop  | 6 2J 2Q 11<br>12 2K -2Q 10 | <b>7</b> |                     |   | σ  |

| 7 | Date<br>Sheet                                               | Doct         |   | CED 2200)                       |                  |  |    |                |                                | L(                         |          |                     |   | 7  |

| 8 | et 3 of 3                                                   | Document N   |   |                                 |                  |  |    |                |                                |                            |          |                     |   | 00 |

|   | Size                                                        | Revision     |   |                                 |                  |  |    |                |                                | <b>.</b>                   | <b>-</b> |                     | r |    |

|   |                                                             | I            | : |                                 | G                |  | רד |                | m                              | Ū                          | n        | œ                   | > |    |