# Reference Solutions: Assignment #1 – ECED 4260

1. A 4-to-1 multiplexer using 2-to-1 multiplexer as components

```

VHDL examples:

```

```

library IEEE;

use IEEE.std logic 1164.all;

entity Mux 4 is

port (

Input : in std logic vector(3 downto 0);

Sel : in std logic vector(1 downto 0);

Output : out std logic

);

end Mux 4;

architecture structural of Mux 4 is

component Mux 2

port(

Input

: in std logic vector(1 downto 0);

Sel : in std_logic;

Output : out std logic

);

end component;

-- Declare the signals needed in the entity

signal internalMuxOut : std logic vector(1 downto 0);

begin

-- Create three Mux 2 components and connect them accordingly

Mux1: Mux_2 port map (Input(3 downto 2), sel(0),internalMuxOut(1));

Mux2: Mux 2 port map (Input(1 downto 0), sel(0), internalMuxOut(0));

Mux3: Mux 2 port map (internalMuxOut(1 downto 0), sel(1),Output);

end structural;

library IEEE;

use IEEE.std logic 1164.all;

pentity Mux 2 is

port (

Input : in std logic vector(1 downto 0);

Sel : in std logic;

Output : out std logic

);

end Mux 2;

architecture rtl of Mux 2 is

-- Declare the signals needed in the entity.

signal sel bar : std logic;

-signal andSel : std logic vector(1 downto 0);

∌begin

sel bar

<= not Sel;

andSel(0) <= sel bar and Input(0);

andSel(1) <= Sel and Input(1);

Output

<= andSel(1) or andSel(0);</pre>

end rtl;

```

### **Verilog MUX:**

```

'timescale 1ns / 1ps

module Mux 4 (

input [3:0] in,

input [1:0] sel,

output out);

// Declare wires needed for entity

wire [1:0] internalMuxOut;

// Create the 3 mux components needed

Mux_2 m1 (in[3:2], sel[0], internalMuxOut[1]);

Mux 2 m2 (in[1:0], sel[0], internalMuxOut[0]);

Mux 2 m3 (internalMuxOut[1:0], sel[1], out);

endmodule

'timescale 1ns / 1ps

module Mux 2 (

input [1:0] in,

input sel,

output out);

wire sel bar;

wire [1:0] andsel;

assign sel bar = \simsel;

assign and sel[0] = sel bar & in[0];

assign and sel[1] = sel & in[1];

assign out = andsel[1] | andsel[0];

endmodule

```

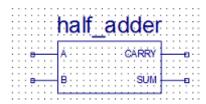

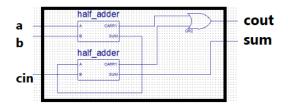

#### **2.** Half Adder and Full Adder:

```

/* Verilog halfadder */

pmodule halfadder (

input a,b,

output Sum, Cout);

assign Sum = a ^ b;

assign Cout = a & b;

endmodule

/* Verilog fulladder */

□module fulladder (

input a,b,cin,

Loutput Sum, Cout);

wire c1, c2, s1;

halfadder HA1 (a, b, s1, c1);

halfadder HA2 (s1, cin, Sum, c2);

assign Cout = c1 | c2;

endmodule

----- VHDL Q3 Full Adder -----

library ieee;

use ieee.std logic 1164.all;

pentity fulladder is

port (a,b, cin: in std logic;

sum, cout : out std logic);

Lend fulladder;

parchitecture structual of fulladder is

component halfadder

port (a,b: in std logic;

sum, carry : out std logic);

end component;

signal c1, c2, s1: std logic;

begin

HA1 : halfadder port map (a, b, s1, c1);

HA2 : halfadder port map (s1, cin, sum, c2);

cout <= c1 or c2;

end structual;

---- VHDL Half Adder -----

library ieee;

use ieee.std logic 1164.all;

pentity halfadder is

port (a,b: in std logic;

sum, carry : out std logic);

lend halfadder;

architecture dtfl of halfadder is

□begin

sum <= a xor b;

carry <= a and b;

end dtfl;

```

3. Design a Binary Coded Decimal (BCD) – to - 7-segment display decoder using VHDL or Verilog. The seven outputs of the decoder, *a* to *g*, are active high (i.e. a '1' will light up the corresponding segment)

```

library ieee;

use ieee.std logic 1164.all;

pentity BCD 7Seg is

port (BCD: in std_logic_vector (3 downto 0);

- a, b, c, d, e, f, g: out std logic);

end BCD_7Seg;

Farchitecture behavioral of BCD 7Seg is

Lsignal Seg: std_logic_vector (6 downto 0);

pbegin

with BCD select

Seg <= "01111111" when "0000",

"0000110" when "0001",

"1011011" when "0010",

"1001111" when "0011",

"1100110" when "0100",

"1101101" when "0101",

"1111101" when "0110",

"0000111" when "0111",

"1111111" when "1000", "1101111" when "1001",

"0000000" when others;

a \leq Seg (0);

b <= Seg (1);

c \le Seg(2);

d \le Seg (3);

e \leq Seg (4);

f \leq Seg(5);

g \le Seg (6);

```

```

88888

88888

```

```

module BCD2 (BCD, a, b, c, d, e, f, g);

input [3:0] BCD;

output a, b, c, d, e, f, g;

reg [6:0] Seg;

always @ (BCD)

□begin

case (BCD)

4'd0 : Seg = 7'b01111111;

4'd1 : Seg = 7'b0000110;

4'd2 : Seg = 7'b1011011;

4'd3 : Seg = 7'b1001111;

4'd4 : Seg = 7'b1100110;

4'd5 : Seg = 7'b1101101;

4'd6 : Seg = 7'b1111101;

4'd7 : Seg = 7'b00000111;

4'd8 : Seg = 7'b11111111;

4'd9 : Seg = 7'b11011111;

default : Seg = 7'b00000000;

endcase

end

assign a = Seg [0];

assign b = Seg [1];

assign c = Seg [2];

assign d = Seg [3];

assign e = Seg [4];

assign f = Seg [5];

assign g = Seg [6];

endmodule

```

.....

end behavioral;

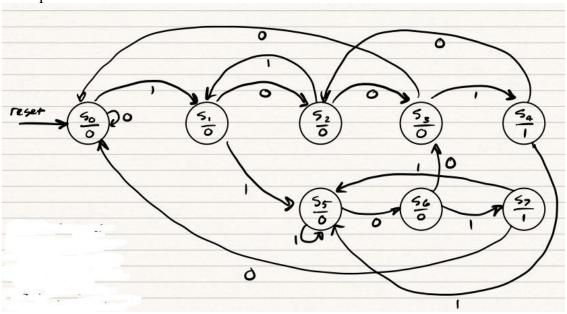

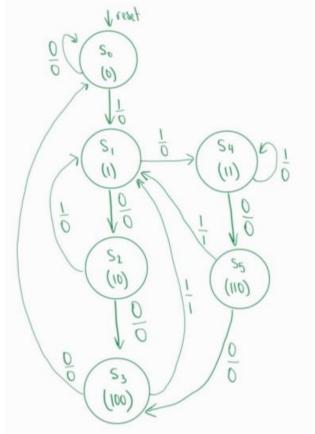

## 4 (a). Reference state diagrams:

Example 1. Moore FSM

Example 2. Mealy FSM

4 (b) (omitted) State optimization, binary state assignment, next-state and output logics.

4 (c)(d) Example Verilog Mealy FSM:

endmodule

```

// overlapping pattern detector module

module overlappingPatternDetector(

input wire clk, // input clock signal

input wire rst, // input reset signal

input wire in, // input bit

output reg out, // output match flag

);

// State encoding

parameter S0 = 3'b000, S1 = 3'b001, S2 = 3'b010,

S3 = 3'b011, S4 = 3'b100, S5 = 3'b101;

// internal variables to store states

reg [2:0] state, next state;

// State transition logic

always @(posedge clk or posedge rst) begin

if (rst)

state <= S0; // Reset state

else

state <= next state; // Move to next state

end

// Next state logic

always @(*) begin

case (state)

S0: next state = (in) ? S1 : S0; // S0 -> S1 if input = 1, else

stay in SO

S1: next state = (in) ? S4 : S2; // S1 -> S4 if input = 1, else

S2

S2: next state = (in) ? S1 : S3; // S2 -> S1 if input = 1, else

S3

S3: next state = (in) ? S1 : S0; // S3 -> S1 if input = 1, else

S0

S4: next state = (in) ? S4 : S5; // S4 -> S5 if input = 0, else

stay in S4

S5: next_state = (in) ? S1 : S3; // S5 -> S1 if input = 1, else

S3

default: next state = S0;

// Default state is S0

endcase

end

// Output logic

always @(posedge clk or posedge rst) begin

if (rst)

out <= 0; // reset output

else

out <= (state == S3 && in) || (state == S5 && in); // Output

logic

end

```

#### **Please note:**

You can code your FSM based on the optimized design from 4 (b): For example:

```

module 1

(clk,rst,I,0);

input clk,rst,I;

output 0;

reg 0;

reg [2:0] state;

parameter s0 = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b101,

s4 = 3'b100;

always@(posedge clk or posedge rst)

begin

if(rst == 1'b1)

begin

state <= s0;

0 <= 1'b0;

end

else

begin

case (state)

s0:

begin

```

• • • • • •

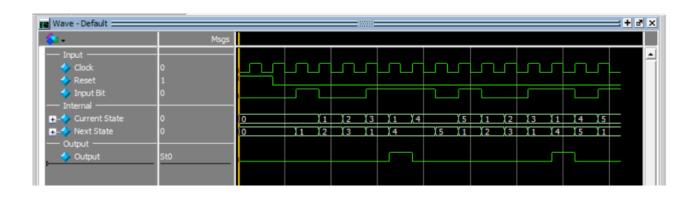

Sample waveform: