- Wafer Manufacturing

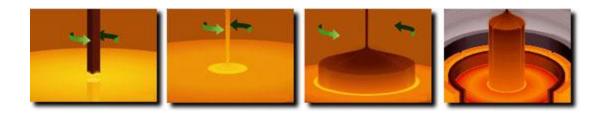

I. Crystal Pulling – Czochralski (CZ) method

- $\bullet$  Doped polycrystalline silicon melted at 1400  $^\circ$

- Inert gas atmosphere of high-purity argon

- Single crystal silicon "seed" is placed into the melt and slowly rotated as it is "pulled out".

- Single crystalline ingot diameter is determined by a combination of temperature and extraction speed.

- The ingots are characterized by the orientation of their silicon crystals. One or two "flats" are ground into the diameter of the ingot.

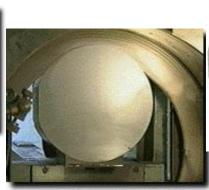

II. Wafer slicing

• After characterization, the ingot is sliced into individual wafers with precision "ID Saw".

Single Crystal Silicon Ingot

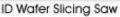

III. Wafer lapping, etching

• The sliced wafers are mechanically lapped using a counterrotating lapping machine and an aluminum oxide slurry to flatten the wafer surface, makes them parallel and reduces mechanical defects.

• Wafers are then etched in a solution of nitride acid / acetic acid to remove microscopic cracks or surface damage followed by a series of high-purity RO/DI water baths.

(Mitsubishi Materials Silicon)

Wafer Polishing (Strasbaugh Corporation)

IV. Wafer polishing and Cleaning

• Next, the wafers are polished in a series of combination chemical and mechanical polishing processes called CMP.

• The polishing process usually involves two or three polishing steps with progressively finer slurry and intermediate cleanings using RO/DI water.

• An SC1 solution (ammonia, hydrogen peroxide and RO/DI water) is used for final cleaning to remove organic impurities and particles. Next, natural oxide and metal impurities are removed with HF and finally SC2 solution causes super clean new natural oxides to grow up on the surface.

V. Wafer epitaxial processing

• A process called epitaxy (EPI) is used to grow a layer of single crystal silicon from vapor onto a single crystal silicon substrate at high temperatures.

• The growth of a single crystalline silicon layer from the vapor phase is called vapor-phase epitaxy (VPE).

## $SiCl_4 + 2H_2 \iff Si + 4HCl$ (*silicontetrachloride*)

The reaction is reversible i.e. if HCl is added Si is etched from the surface of the wafer. Another non-reversible reaction that produces Si is,

$SiH_4 \rightarrow Si + 2H_2$ (silane)

• The purpose of EPI growth is to create a layer with different, usually lower, concentration of electrically active dopant on the substrate. For example, an n-type layer on a p-type wafer.

• Approx. 3% of wafer thickness.

Contamination free for the subsequent construction of tranisistors.

**Epitaxial Reactor** (Mitsubishi Materials Silicon)

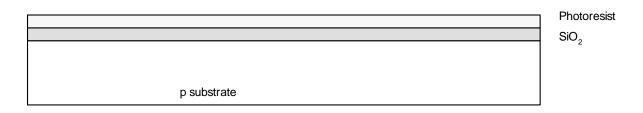

## - Photolithography

## I. Photoresist coating

• Photoresist is a photo-sensitive material applied to the wafer in a liquid state in small quantities. The wafer is spun at 1000 to 5000 rpm which spreads the "puddle" into a uniform layer between 2 and 200  $\mu$ m thick.

• There are two types of photoresist: negative and positive.

- positive – exposure to light breaks down complex molecular structure, making it easy to be dissolved.

- negative – exposure to light causes molecular structure to become more complex and more difficult to be dissolved.

The steps involved in each photolithography step are as follows;

- clean wafers

- deposit barrier layer SiO<sub>2</sub>,

Si<sub>3</sub>N<sub>4</sub>, Metal

- coat with photoresist

- soft bake

- align masks

- expose pattern

- develop photoresist

- hard bake

- etch windows in photoresist

- remove photoresist

Photoresist Application (Ontrak)

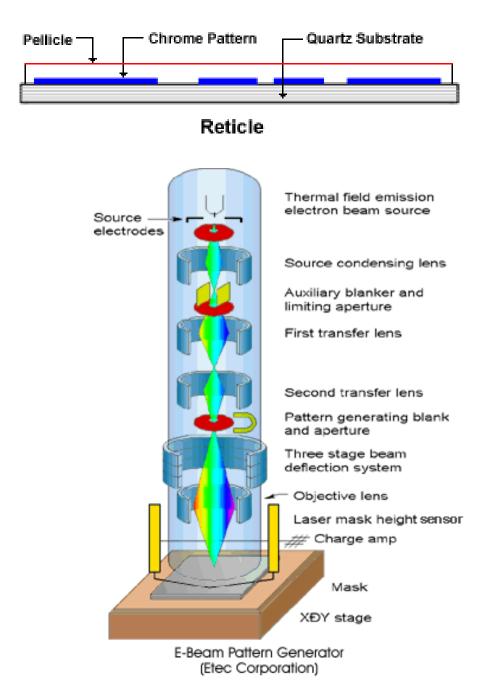

### **II.** Pattern Preparation

• IC designers design the pattern for each layer using CAD software. The pattern is then transferred to an optically clear quartz substrate (reticle) with a chrome pattern using a laser pattern generator or an e-beam.

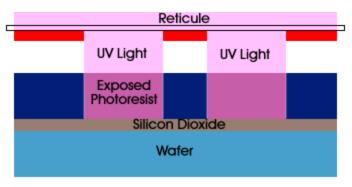

III. Device layer pattern transfer

• Applying and exposing photoresist to create a device layer on an actual wafer is similar to the process used to create reticles. For actual production, a tool called stepper is used.

Exposure

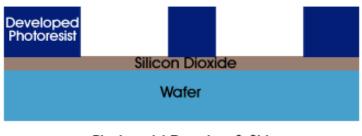

### III. Develop and Bake

• After exposure, wafers are developed in either an acid or base solution to remove the exposed areas of photoresist.

• Once the exposed photoresist is removed, the wafer is "soft-baked" at a low temperature to harden the remaining photoresist.

Photoresist Develop & Strip

\* Dust particles are the main concern in the photolithography process. Room air quality is measured by Class i.e. a Class 10 room has less than 10 dust particles of size greater than 0.5µm per cubic foot of air. In order to avoid contamination of the wafer surface with dust particles wafer processing is carried out in clean rooms.

- Etching and Ion Implantation

- I. Wet and Dry Etch

• Etching with chemicals takes place at large wet benches.

•Different types of acid, base and caustic solutions are used for removing selected areas of different material.

• BOE, or buffered oxide etch, prepared from hydrofluoric acid buffered with ammonium fluoride is used to remove silicon dioxide without etching away underlying silicon or polysilicon layer.

- Phosphoric acid is used to etch silicon nitride layers.

- Nitric acid is used to etch metals.

- Sulfuric acid is used to remove photoresist.

- For dry etch, the wafer is placed into an etching chamber and etching is done by plasma.

- Personnel safety is a primary concern.

- Many fabs use automated equipment perform the etching process.

II. Photoresist strip

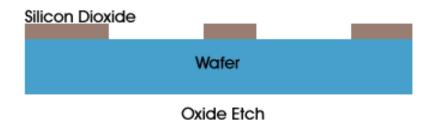

• The photoresist is then completely stripped off the wafer, leaving the oxide pattern on the wafer.

### III. Ion Implantation

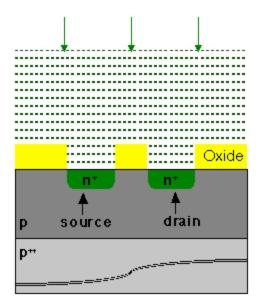

• Ion implantation changes the electrical characteristics of precise areas within an existing layer on the wafer.

• An ion implanter uses a high-current accelerator tube and steering and focusing magnets to bombard the surface of the wafer with ions of a particular dopant.

• For the MOSFET example, the oxide acts as a barrier when dopant chemicals are deposited on the surface and diffused into the surface.

• Annealing is done by heating the silicon surface to 900°C. The implanted dopant ions diffuse further into the silicon wafer.

# The Semiconductor Manufacturing Process - Thin Film Deposition

I. Silicon oxidation

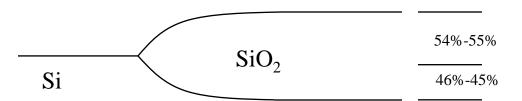

$SiO_2$  grows thermally when silicon is in the presence of oxygen. Oxygen comes from oxygen gas or water vapor. A temperature of 900 to 1200 °C is required.

The chemical reactions that occur are

- $Si + O_2 \rightarrow SiO_2$

- $Si + 2H_2O -> SiO_2 + 2H_2$

• The surface of the silicon wafer after selective oxidation will appear as follow,

• Both oxygen and water will diffuse through the existing  $SiO_2$  and combine with Si to form additional  $SiO_2$ . Water (steam) diffuses easier than oxygen, hence there is a much faster growth rate with steam.

• Oxide is used to provide insulating and passivation layers and form transistor gates. Dry O2 is used to form gates and thin oxide layers. Steam is used to form thick oxide layers. Insulating oxide layers are usually about 1500 Å and gate layers are usually between 200 Å to 500 Å.

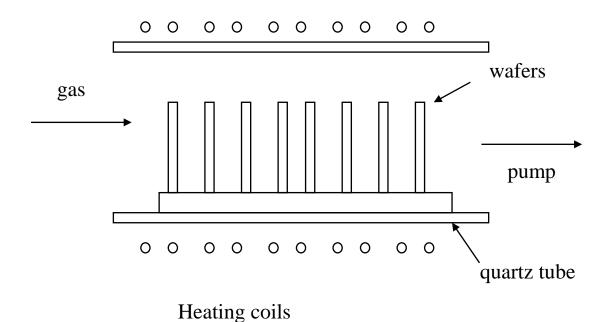

#### **II. Chemical Vapor Deposition**

• Chemical Vapor Deposition (CVD) forms thin films on the surface of the substrate by either thermal decomposition and/or reaction of gaseous compounds.

- There are three basic types of reactors for CVD,

- atmospheric chemical vapor deposition

- low pressure CVD (LPCVD)

- plasma enhanced CVD (PECVD)

- A sketch of a Low Pressure CVD process is show below,

## i) Polysilicon

$SiH_4 \rightarrow Si + 2 H_2$

Deposits 100 to 200 Å /min

- Phosphorous (phosphine), Boron (Diborane) or Arsenic gases can be addded. Polysilicon can also be doped with diffusion gases after it has been deposited.

- ii) Silicon Dioxide

300 to 500°C

$SiH_4 + O_2 \rightarrow SiO_2 + 2H_2$

• SiO2 is used as an insulator or passivation layer. Usually phosphorous is added to give better 'flow' properties.

## iii) Silicon Nitride

$3SiH_4 + 4NH_3 \rightarrow Si_3N_4 + 12 H_2$ (silane) (ammonia) (nitride)

# **III. Sputtering**

If a target is bombarded with high energy ions such as Ar+ then atoms in the target will be dislodged and transported to the substrate.

Metals such as Al, Ti can be used as a target.

## **IV. Evaporation**

If Al or Au (gold) is heated to the point of evaporation then the vapor will condense and form a thin film that covers the surface of the wafer.

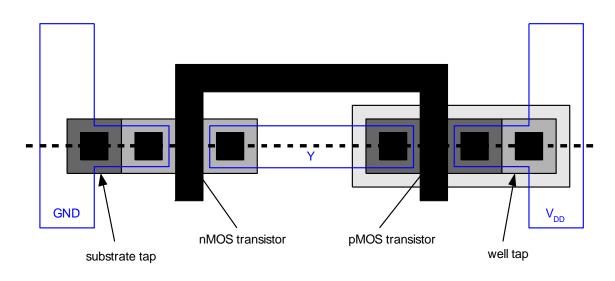

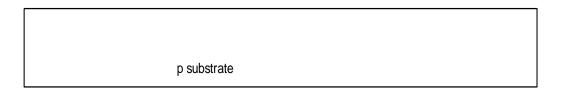

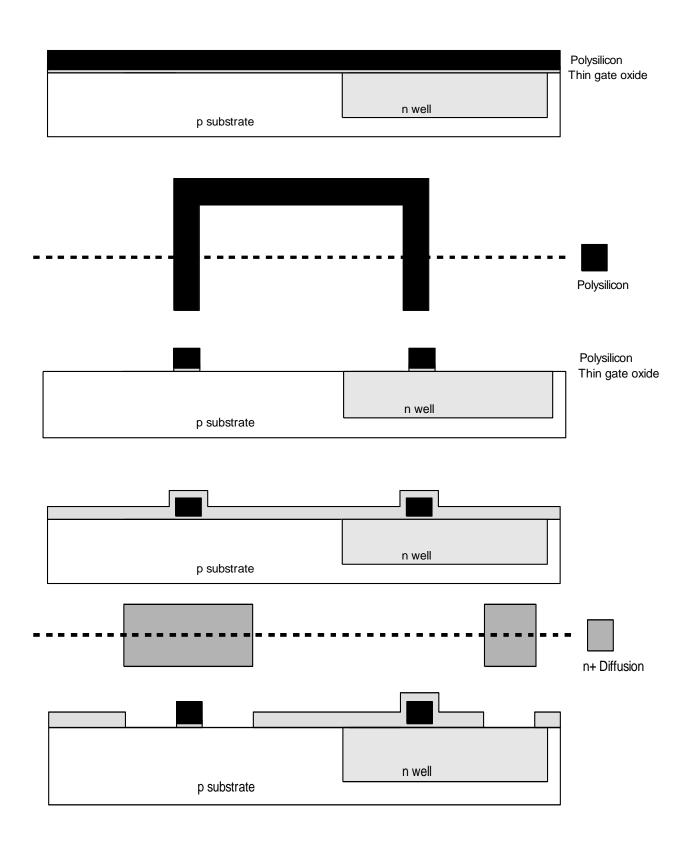

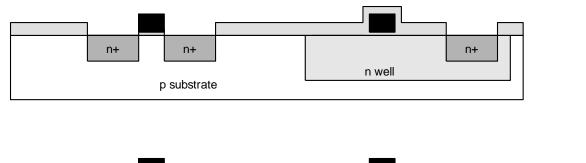

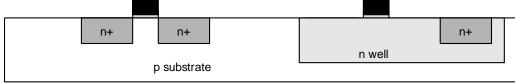

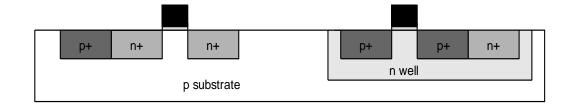

# Example: Inverter Mask Set

|              | SiO <sub>2</sub> |

|--------------|------------------|

|              |                  |

| n quipetroto |                  |

| p substrate  |                  |

|             |          | Photoresist      |

|-------------|----------|------------------|

|             |          | SiO <sub>2</sub> |

| p substrate |          |                  |

|             |          |                  |

|             |          | Photoresist      |

|             |          | SiO2             |

| p substrate |          |                  |

|             |          |                  |

|             |          | SiO <sub>2</sub> |

| p substrate |          |                  |

|             |          |                  |

|             | <u> </u> | SiO2             |

|             | n well   | L                |

|             |          |                  |

| Γ           | 1        |                  |

|             | n well   |                  |

| p substrate |          |                  |

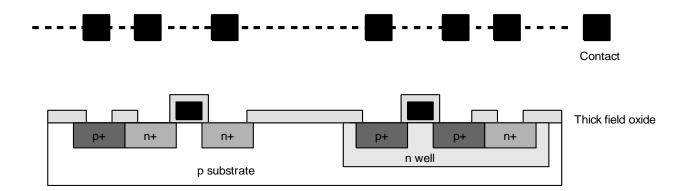

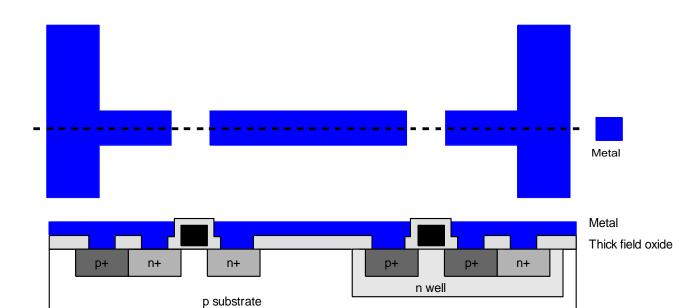

- Six masks

- n-well

- Polysilicon

- n+ diffusion

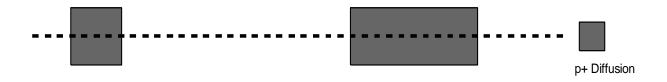

- p+ diffusion

Contact

Metal

Polysilicon

p+ Diffusion

p+ Diffusion

Contact

Generating

- Post-processing

I. Probe Test and Wafer Dicing

• After the final passivation layer and backside prep, automated methods are used to test the device on the wafer.

• A probe tester is used to check the operation of the device. Devices that fail the test are marked with colored dye.

• After probe test, the wafer is diced into individual die.

II. Wire Bonding and Packing

• Individual devices are attached to a lead frame and aluminum or gold leads are attached via thermal compression or ultrasound welding.

• The packaging is completed by sealing the device into a ceramic or plastic package.

Wire Bonding (Kulicke & Soffa Industries, Inc.)

Wire Bonding (Kaijo Corporation)

Packaging