## **Unit 6. Writing Testbenches**

- 6.1 The Importance of Verification

- 6.2 Verification Tools

- 6.2.1 Logic Simulation Overview

- 6.2.2 True Value Simulation

- 6.2.3 Event-Driven Simulation

- 6.3 Behavioral HDL

- 6.4 Writing Testbenches

# 6.1 The Importance of Verification

- Verification is a process used to demonstrate the functional correctness of a design.

- Verification is not a testbench, nor is it a series of testbenches.

What is a testbench?

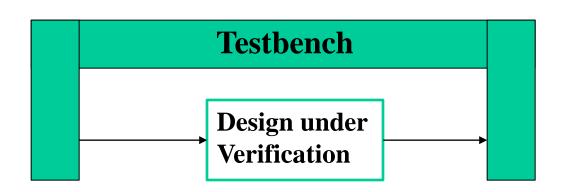

• The term "testbench", in VHDL and Verilog, usually refers to the code used to create a pre-determined input sequence to a design, then optionally observe the response.

# 6.1 The Importance of Verification (cont'd)

- Verification consumes about 70% of the design effort.

- Verification is on critical path.

- Verification time can be reduced through parallelism. To parallelize the verification effort, it is necessary to be able to write-and debug- testbenches in parallel with each other as well as in parallel with the implementation of the design.

- Using abstraction reduces control over low-level details. Verification time can be reduced through automation.

## 6.2: Verification Tools

Different kinds of verification tools can be used to verify different aspect of the design and identify different types of errors.

- Linting tools

- Simulators

- Waveform viewers

- Code coverage analysis

- Revision control and issue tracking

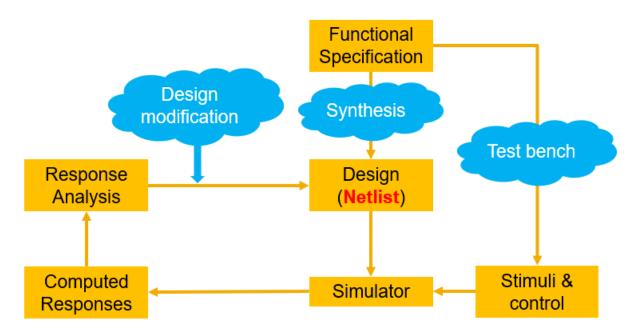

## Simulator

- A tool for design verification testing;

- Ascertain a design perform its specified behavior (function and timing)

### Logic Simulation Overview

## 6.2.1 Logic Simulation Overview

**Netlist**: a format (or language) that describes a design as an interconnection of modules. Netlist may use hierarchy.

## Modules, blocks or components described by:

- I/O functions

- Delays associated with I/O signals

- Examples: FET, resistors, capacitors, gates, adder etc.

**Interconnectors** represent:

• Ideal signal carriers or ideal electrical conductors

## 6.2.2 True Value Simulation

Determine the output for certain inputs Find design errors, timing problems, etc.

Limitations:

- The set of design errors is not enumerable

- No formal procedure to generate tests

- A system passes the test is shown correct only with the applied test cases

- Simplified circuit model

- A circuit passes the simulation test may not work when being wired up

# 6.2.2 True Value Simulation (cont'd)

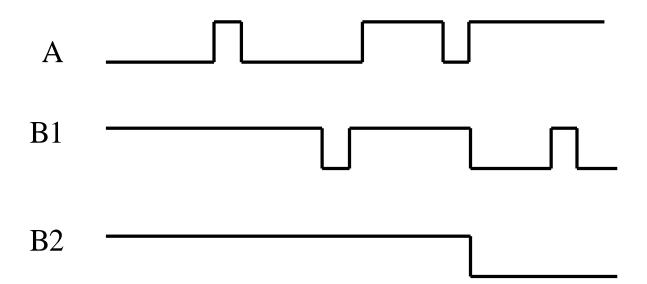

## Timing : delay models in VHDL

- Transport delays

- Initial delays

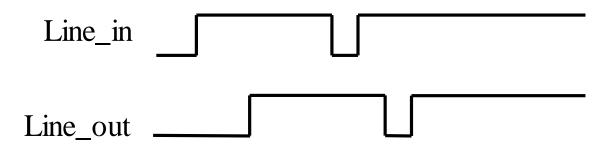

### **Transport delay:**

- Model transmission lines.

- Line\_out <= transport line\_in after 3 ns;

- Remarks: Output is assigned with specified delay independently from the width of the pulse in waveform.

### **Inertial delay (default):**

- Model the devices. Default delay model implemented in VHDL.

- Line\_out <= inertial not line\_in after 3 ns;

- Line\_out <= **not** line\_in **after** 3 ns;

- Line\_out <= reject 500ps inertial not line\_in after 3 ns;

- Remarks: Impulses shorter than the specified switching time are not transmitted.

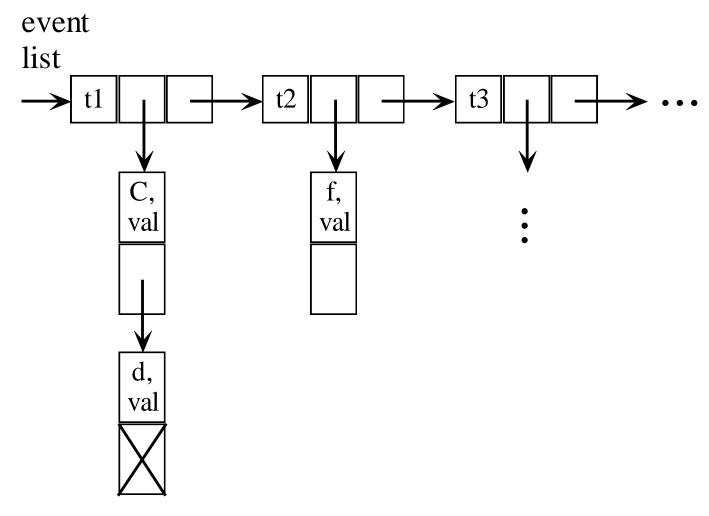

## 6.2.3 Event-driven Simulation

- General concept behind most simulation algorithms

- An event represents a change in the value of a signal line at some simulated time t

- If the value of a signal line x changes, then all gates having x as input are activated

- If the activated gates change their output values, new events are generated.

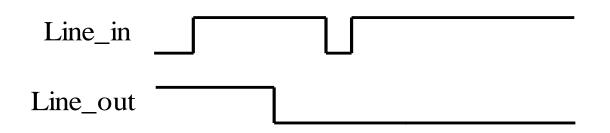

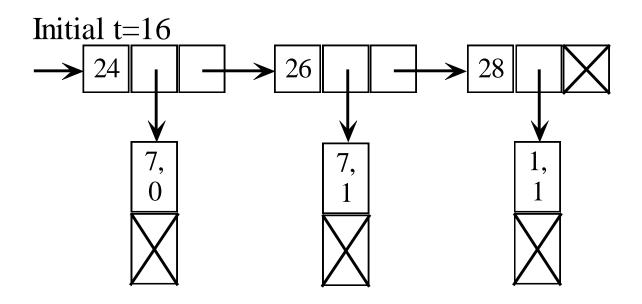

## 6.2.2 Event\_driven Simulation (cont'd)

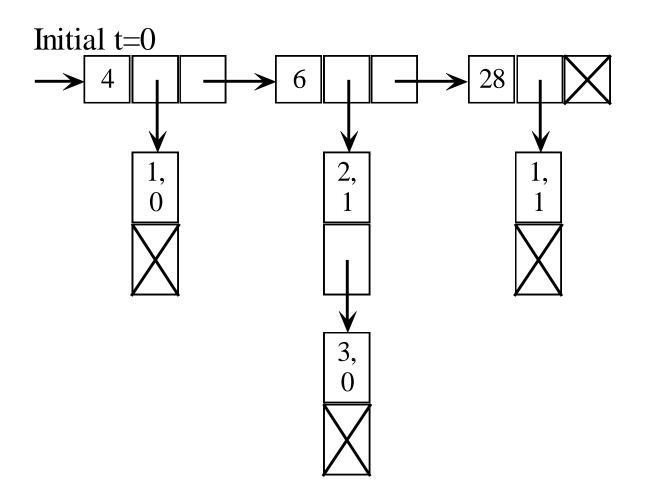

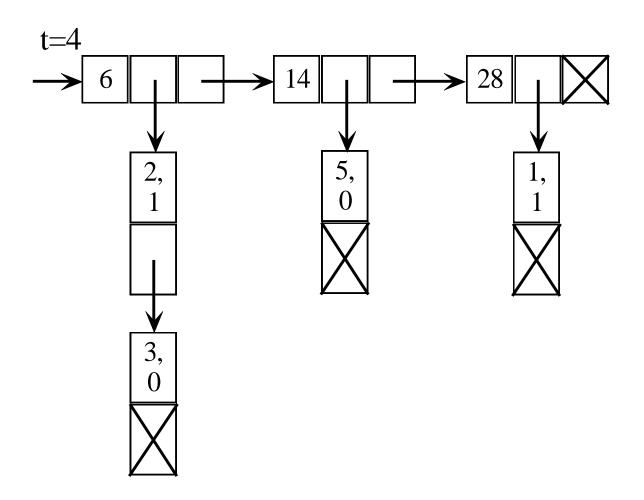

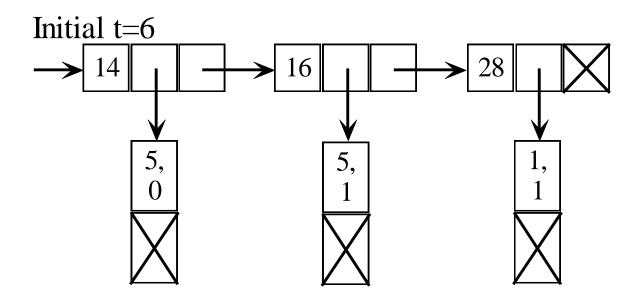

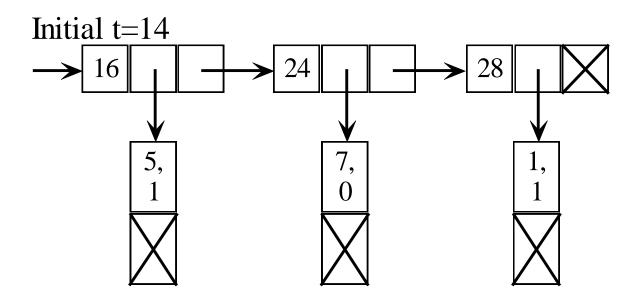

• An event list can be organized as a linked list stored in increasing time order

## 6.2.2 Event\_driven Simulation (cont'd)

Two-pass algorithm for gate-level event-driven simulation While(event\_list is not empty) do begin For (every event(x,val) at time t) do begin Get the event (x,val) If(current\_val\_of\_x <>val) then begin Current\_val\_of\_x=val For (each gate J on fanout list of x) do begin Change the value of fanout line going into gate J

Add gate J to activated\_gates

End

End

#### End

For (each gate J of activated\_gates) do begin

Compute output value of gate J

$\label{eq:last_scheduled_value_gate_j} If (output_value_gate_j <> last_scheduled_value_gate_j) \ then \ begin$

Schedule (output\_line\_number\_gate\_J,output\_value\_gate\_J) for time t+delay of gate\_J

#### Last scheduled\_value\_gate\_J=output\_value\_gate\_J End

End

#### End

## 6.2.2 Event\_driven Simulation (cont'd)

- Pass1

- Get the entries from the event list associated with the current time t

- Determine the activated gates

- This is to avoid multiple evaluations of a gate that is activated by more than one event

- Pass2

- Compute the new output values of the activated gates

- Schedule their computed value in the event list

- The algorithm keeps track of the last-scheduled value of a gate so as to schedule only "true" events

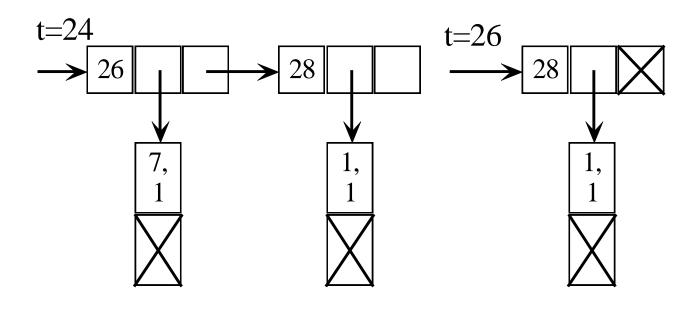

| Gate              | A     | В    | С     |

|-------------------|-------|------|-------|

| Propagation delay | 10 ns | 6 ns | 10 ns |

|      | Phase 1     |   |   |   |   |   |   | phase2            |   |   |                  |

|------|-------------|---|---|---|---|---|---|-------------------|---|---|------------------|

|      | Line values |   |   |   |   |   |   | Gates<br>affected |   |   | Scheduled events |

| Time | 1           | 2 | 3 | 4 | 5 | 6 | 7 | A                 | В | C |                  |

| Init | 1           | 0 | 1 | 0 | 1 | 0 | 1 |                   |   |   |                  |

| 4    | 0           |   |   |   |   |   |   | X                 |   |   | (5,0) at 4+10    |

| 6    |             | 1 | 0 | 1 |   |   |   | X                 | Χ |   | (5,1) at 6+10    |

| 14   |             |   |   |   | 0 |   |   |                   |   | X | (7,0) at 14+10   |

| 16   |             |   |   |   | 1 |   |   |                   |   | X | (7,1) at 16+10   |

| 24   |             |   |   |   |   |   | 0 |                   |   |   |                  |

| 26   |             |   |   |   |   |   | 1 |                   |   |   |                  |

| 28   | 1           |   |   |   |   |   |   | X                 |   |   |                  |

### Event\_driven Simulation (cont'd): Timing Diagram

## 6.3: Behavioral HDL

**RTL** coding guidelines help designer obtain efficient implementations: low area, high speed, or low power.

To avoid undesirable hardware structures:

- To avoid latches, set all outputs of combinational blocks to default values at the beginning of the block;

- To avoid tristate buffers, do not assign the value 'Z'.

**T**o maintain simulation behavior:

- All inputs must be listed in the sensitivity list of a combinational block;

- The clock and asynchronous reset must be in the sensitivity list of a sequential block.

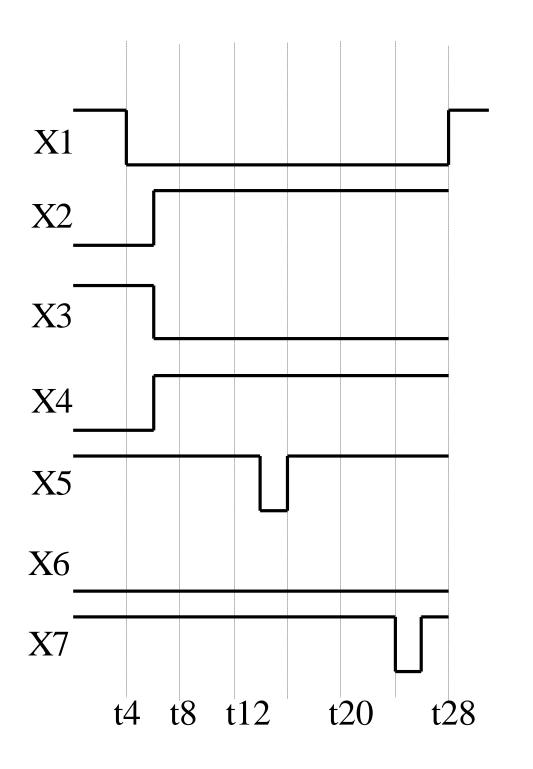

Example: State diagram for handshaking protocol

### **Behavioral VHDL:**

```

process

begin

```

. . .

REQ <= '1'; Wait until ACK = '1'; REQ <= '0'; Wait until ACK = '0';

end process;

## Synthesizable VHDL code

**Type** state\_typ **is** (..., make\_req, release,...); **Signal** state, next\_state: state\_typ;

```

COMB: process (state, ACK)

begin

next state <= state;

case state is

. . .

when make_req =>

Req <= '1';

if ACK ='1' then

Next_state <= release;

end if:

when release =>

Req <= '0';

if ACK ='0' then

SEQ: process (CLK)

Next sate <=...;

begin

end if;

if clk'event and clk='1' then

. . .

if reset = '1' then

end case;

state <= ...;

else

end process COMB;

state <= next_state;</pre>

end if:

end if;

end process SEQ;

```

## Connectivity, Time and Concurrency

- Connectivity is the ability of describing a design using simpler blocks then connecting them together.

- Time is the ability to represent how the internal state of a design evolves over time.

- Concurrency is the ability to describe actions that occur at the same time, independently of each other.

## 6.4 Writing Test-Benches

- Generating a Simple Waveform

LIBRARY ieee; USE ieee.std\_logic\_1164.all; USE ieee.std\_logic\_signed.all;

ENTITY testbench IS END testbench;

**ARCHITECTURE Behavior OF testbench IS**

COMPONENT Addern PORT (X, Y : IN STD\_LOGIC\_VECTOR(15 DOWNTO 0); Cin : IN STD\_LOGIC; S : OUT STD\_LOGIC\_VECTOR(15 DOWNTO 0); Cout : OUT STD\_LOGIC ); END COMPONENT;

```

SIGNAL Cin : STD LOGIC;

SIGNAL X : STD_LOGIC_VECTOR(15 DOWNTO 0);

SIGNAL Y : STD_LOGIC_VECTOR(15 DOWNTO 0);

SIGNAL S : STD LOGIC VECTOR(15 DOWNTO 0);

SIGNAL Cout : STD_LOGIC;

BEGIN

vectors: PROCESS

BEGIN

X <= X''0000'': Y <= X''0000'': Cin <= '0':

WAIT FOR 20 ns;

Y <= X''000A''; Cin <= '0';

WAIT FOR 20 ns;

X <= X''000A''; Cin <= '0';

WAIT FOR 20 ns;

Cin <= '1';

WAIT FOR 20 ns;

X <= X''FFF0''; Y <= X''000F''; Cin <= '0';

WAIT FOR 20 ns;

Cin <= '1';

WAIT;

```

**END PROCESS;**

U1: Addern PORT MAP (X, Y, Cin, S, Cout); END; LIBRARY ieee; USE ieee.std\_logic\_1164.all; USE ieee.std\_logic\_signed.all;

ENTITY testbench IS END testbench;

**ARCHITECTURE Behavior OF testbench IS**

COMPONENT Accumulate PORT ( KEY : IN STD\_LOGIC\_VECTOR(0 DOWNTO 0); SW : IN STD\_LOGIC\_VECTOR(9 DOWNTO 0); CLOCK\_50 : IN STD\_LOGIC; LEDR : OUT STD\_LOGIC\_VECTOR(9 DOWNTO 0)); END COMPONENT;

> SIGNAL CLOCK\_50 : STD\_LOGIC; SIGNAL KEY : STD\_LOGIC\_VECTOR(0 DOWNTO 0); SIGNAL SW : STD\_LOGIC\_VECTOR(9 DOWNTO 0); SIGNAL LEDR : STD\_LOGIC\_VECTOR(9 DOWNTO 0);

#### BEGIN

U1: Accumulate PORT MAP (KEY, SW, CLOCK\_50, LEDR);

```

clock process: PROCESS

BEGIN

CLOCK_50 <= '0';

WAIT FOR 10 ns;

CLOCK_50 <= '1';

WAIT FOR 10 ns;

END PROCESS;

vectors: PROCESS

BEGIN

KEY(0) <= '0'; SW <= "0000000000";

WAIT FOR 20 ns;

SW(9 DOWNTO 5) <= "01010";

WAIT FOR 20 ns;

SW(4 DOWNTO 0) <= "11110";

KEY(0) <= '1';

WAIT;

END PROCESS:

```

30

LIBRARY ieee; USE ieee.std\_logic\_1164.all; USE ieee.std\_logic\_signed.all;

ENTITY testbench IS END testbench;

```

ARCHITECTURE Behavior OF testbench IS

COMPONENT display

PORT ( KEY : IN STD_LOGIC_VECTOR(0 DOWNTO 0);

SW : IN STD_LOGIC_VECTOR(0 DOWNTO 0);

HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

LEDR : OUT STD_LOGIC_VECTOR(9 DOWNTO 0));

END COMPONENT;

```

```

SIGNAL KEY : STD_LOGIC_VECTOR(0 DOWNTO 0);

SIGNAL SW : STD_LOGIC_VECTOR(0 DOWNTO 0);

SIGNAL HEX0 : STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL LEDR : STD_LOGIC_VECTOR(9 DOWNTO 0);

BEGIN

```

U1: display PORT MAP (KEY, SW, HEX0, LEDR);

```

clock process: PROCESS

BEGIN

KEY(0) \le '0';

WAIT FOR 10 ns;

KEY(0) <= '1';

WAIT FOR 10 ns:

END PROCESS:

vectors: PROCESS

BEGIN

-- Resetn = 0

SW(0) <= '0':

WAIT FOR 20 ns;

-- Resetn = 1

SW(0) <= '1':

WAIT;

END PROCESS;

END:

```